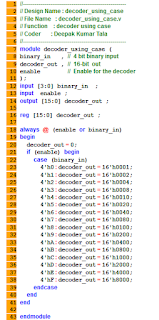

Decoder using case statement

Pada program tersebut kita membuat kodingan untuk Decoder dengan menggunakan Case statament. Penggunaan // adalah untuk memberikan komentar perbaris.

Module decoder_using_case merupakan penamaan untuk module yang akan kita buat.

Pada baris 8 menunjukan inputan yang diberi nma binary_in dan baris 9 merupakan output bernama decoder_out

Pada decoder dijelaskan baris 12 bahwa input terdiri dari 4 bit dimana dimulai dari bit0 sampai bit3. Untuk outputnya terdiri dari 16 output dari 0 sampai 15.

Dibaris 20 untuk output pertama decoder output adalah 0 selanjutnya jika input h0 maka outputnya satu. Saat input h1 maka outputnya 2. Input disini merupakan nilai biner dlan pada outputnya menjadikannya bentuk desimal. Sampai output berakhir pada h8000

Berikut adalah kodingan untuk mux dengan menggunakan case statemen

Pada mux ini terdapat 2 buah inputan yaitu din_0 dan din_. Untuk output bernama mux_out. Pada mux terdapat selector atau sel yang berungsi untuk memilih jalur input menuju outputnya.

Pada baris 22 menentukan selector. Sat biner 0 tau b0 makan input pada din_0 dan jika selector bi maka inputnya melalui din_1.

Mux ini merupakan rangkaian dengan banyak input manamun hanya 1 keluaran.

Berikutnya ada kodingan untuk asynchronous reset D-Flip flop. Awalnya kita membuat nama module dengan dff_async_reset. Untuk penamaan bebas

Sebagai input ada'data' dan clk' serta untuk output kita gunakan Q. Q juga sebagai reg atau register

Pada baris 23 merupakan clock yang akan digunakan karena pada setiap flip flop pasti ada clock sebagai pacu atau denyut input per sekian detik.

Jika invers dari reset maka outputnya bernilai b0 namun jika sebaliknya maka outpu sesuai dengan data input.

End untuk mengahiri program.

Berikut ini adalah program untuk Up counter atau mencacah nilai secara berurut dari terkecil ke terbesar.

Untuk penamaan modulenya adalah up_counter. Dengan 'out ' sebagai nama untuk keluaran. Untuk masukannya didpat dari clk, reset dan enable.

Output terdiri dari 8 bit dari 0-7. Untuk register atau penyimpanannya juga sama 0-7.

Di up counter ini terdapat clk yang aktif. Jika pada keaadan reser maka output akan keluar pada b0 namun jika kondisi tersebut tidak sesuai makan outunta akan bertambah 1. Secara berurut dari terkecil hingga terbesar.

Ini merupakan suatu program untuk memori ROM. Seperti biasa kita membuat module dengan penamaan bebas, disini menggunakan rom_using_case. Sebagai inputannya ada addres atau alamat, outputnya berupa data. Kemudian disambungkan juga dengan read_en dan ce atau chip

Untuk adders terdiri dari 4 bit dan output data 8 bit. Data sebagai register sebesar 8 bit. Selalu terdapat cloc pada baris 20 karena selalu ada perubahan pada clocknya.

Pada baris 22 merupakan awal mengalamatan emmroi rom. Jika inputnya 0 maka output 10, jka inputnya 1 makan outputnya 55. Begitu seterusnya sesuai dengan input yang masuk.

Parity dengan Assign. Disini kita mebuat module dengan nama parity_using_assign. Dengan input bernama 'data_in' terdiri dari 8 bit dari 0-7. Dan outputnya bernama 'parity_out' dengan hanya 1 bit.

Untuk mendaparkan oitputya dengan memangkatkan data datanya. Datain[0] atau data pertama dipangkat datain[1] dipangkatka lagi dengan data in[3], begitu seterusnya sampai data terakhir yaitu data in7 sebagai bit terakhir.

Tidak ada komentar:

Posting Komentar